Articles

DS ISE 1

- Détails

- Catégorie : Notions de VHDL

Sommaire[Masquer]

1. Présentation du sujet

On réalise un système comptant de 10 à 15 et affichant une lettre, de A à F, pour chacun de ces nombres.

1.1. Première partie : système combinatoire

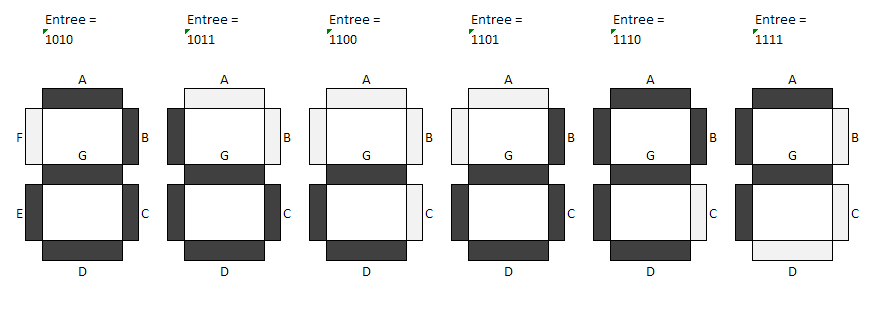

Il s'agit de réaliser un décodeur 7 segments restreint aux lettres hexadécimales en langage VHDL.

L'entrée se réalise sur 4 bits. On note \(Entree_{0}\) le bit de poids faible et \(Entree_{3}\) le bit de poids fort. On aura 7 sorties (A, B, C, D, E, F, G) pour l'ensemble des segments.

- Créer un projet sous Xilinx ISE pour cibler le FPGA de la Basys 2 (nom du projet : votre nom).

- Créer le module decodeur_lettres.vhd dans un dossier à votre nom placé sur le bureau.

- Avec l'approche de votre choix, écrire le programme VHDL permettant de réaliser le décodeur souhaité.

- Ecrire un fichier de test du décodeur (vous pouvez utiliser le programme pour générer les fichiers de test).

1.2. Seconde partie : système séquentiel

- Il s'agit maintenant, dans le même projet, de réaliser un compteur comptant de 10 à 15 (valeur initiale 10).

- Ecrire le programme d'un tel compteur avec Reset asynchrone prioritaire.

- Ecrire le programme de test pour présenter des tests pertinents.

1.3. Dernière partie : schéma de l'ensemble

- Réaliser le schéma de l'ensemble en ajoutant un nouveau fichier au projet (type Schematic/Bloc diagram).

- Ecrire un programme de test pour montrer le fonctionnement de l'ensemble.